Intel Agilex Logic Array Blloqe dhe Modulet Adaptive Logic

Intel® Agilex™ LAB dhe ALM Overview

Blloku i grupit logjik (LAB) është i përbërë nga blloqe ndërtimi bazë të njohur si module logjike adaptive (ALM). Ju mund të konfiguroni LAB-të për të zbatuar funksione logjike, funksione aritmetike dhe funksione të regjistrimit.

Ju mund të përdorni gjysmën e LAB-ve të disponueshme në pajisjet Intel® Agilex™ si LAB me memorie (MLAB). Disa pajisje mund të kenë një raport më të lartë MLAB.

Softueri Intel Quartus® Prime dhe mjete të tjera të mbështetura të sintezës së palëve të treta zgjedhin automatikisht modalitetin e duhur për funksionet e zakonshme si numëruesit, grumbulluesit, zbritësit dhe funksionet aritmetike.

Arkitektura kryesore e Intel Hyperflex™, Pajisja Intel Agilex përfundoiview

Ofron më shumë informacion rreth Hyper-Registers dhe arkitekturës bazë Intel Hyperflex™. Hiper-Regjistruesit janë regjistra shtesë të disponueshëm në çdo segment të rrugëzimit të ndërlidhjes në të gjithë strukturën bazë, duke përfshirë segmentet e rrugëtimit të lidhur me hyrjet dhe daljet LAB.

Regjistrohu Intel Hyperflex™

Familja e pajisjeve Intel Agilex bazohet në arkitekturën bazë të Intel Hyperflex™.

Intel Agilex LAB përmban regjistra Intel Hyperflex dhe veçori të tjera të krijuara për të lehtësuar ricaktimin e kohës. Regjistrat Intel Hyperflex janë të disponueshëm në ALM dhe zinxhirë transportues. Siç tregohet në figurën e Detajeve të Lidhjes ALM të Intel Agilex, regjistrat e Intel Hyperflex janë të vendosura në pastruesin sinkron dhe ora mundëson hyrjet për të rritur ose zvogëluar vonesën e rrugës. Të gjithë regjistrat Intel Hyperflex mund të aktivizohen dhe kontrollohen nga softueri Intel Quartus Prime gjatë ri-kohës.

Arkitektura dhe veçoritë e Intel Agilex LAB dhe ALM

Seksionet e mëposhtme përshkruajnë LAB dhe ALM për pajisjet Intel Agilex.

LAB

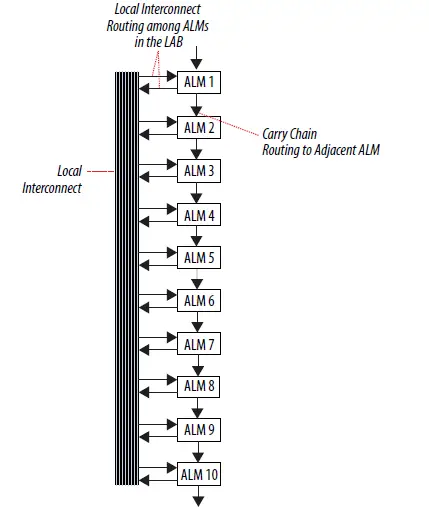

LAB-të janë blloqe logjike të konfigurueshme që përbëhen nga një grup burimesh logjike. Çdo LAB përmban logjikë të dedikuar për sinjalet e kontrollit të drejtimit të ALM-ve të tij. MLAB është një superbashkësi e LAB dhe përfshin të gjitha tiparet LAB. Ka gjithsej 10 ALM në çdo LAB, siç tregohet në figurën e Intel Agilex LAB dhe MLAB Structure.

Figura 1.

Struktura dhe ndërlidhja e Intel Agilex LABview

Kjo shifër tregon një mbiview të strukturës Intel Agilex LAB dhe MLAB me ndërlidhjet LAB.

Informacione të Përafërta

Informacione të Përafërta

MLAB në faqen 6

MLAB

Çdo MLAB mbështet një maksimum prej 640 bit SRAM të thjeshtë me dy porte. Ju mund të konfiguroni çdo ALM në një MLAB si një bllok memorie 32 (thellësi) x 2 (gjerësi), duke rezultuar në një konfigurim prej 32 (thellësi) x 20 (gjerësi) bllok të thjeshtë SRAM me dy porta.

Figura 2.

Struktura Intel Agilex LAB dhe MLAB Ndërlidhjet e Lidhjeve Lokale dhe Direkte

Ndërlidhjet e Lidhjeve Lokale dhe Direkte

Çdo LAB mund të nxjerrë 60 dalje ALM. Një nëngrup i tyre mund të drejtojë drejtpërdrejt hyrjet LAB, por çdo lidhje me një rresht ose kolonë tjetër duhet të përdorë të paktën një tel drejtimi për qëllime të përgjithshme.

Ndërlidhja lokale drejton hyrjet ALM. Daljet ALM, si dhe ndërlidhjet e kolonave dhe rreshtave drejtojnë ndërlidhjen lokale.

Figura 3. Interconnect Local dhe Direct Link Intel Agilex LAB  Mbajtja e ndërlidhjeve të zinxhirit

Mbajtja e ndërlidhjeve të zinxhirit

Ekziston një rrugë e dedikuar zinxhiri transporti midis ALM-ve. Pajisjet Intel Agilex përfshijnë një strukturë të përmirësuar të ndërlidhjes në LAB për kursimin e zinxhirëve mbajtës për funksione aritmetike efikase. Këto lidhje ALM-to-ALM anashkalojnë ndërlidhjen lokale.

Regjistrat Intel Hyperflex shtohen në zinxhirin mbajtës për të mundësuar ri-kohë fleksibël përgjatë një zinxhiri LAB dhe Kompletuesi Intel Quartus Prime automatikisht merr përparësitage nga këto burime për të përmirësuar përdorimin dhe performancën.

Figura 4. Mbajtja e ndërlidhjeve të zinxhirit Sinjalet e kontrollit LAB

Sinjalet e kontrollit LAB

Ekzistojnë dy burime të orës në çdo bllok kontrolli LAB, të cilat gjenerojnë dy orë LAB (LABCLK[1:0]) dhe dy orë LAB të vonuara (LABCLK_Phi1[1:0]) për të drejtuar regjistrat ALM dhe hiper-regjistrat në LAB. LAB mbështet dy sinjale unike të aktivizimit të orës, si dhe sinjale shtesë të qarta, për regjistrat ALM.

Orët e rreshtit LAB [5..0] dhe ndërlidhjet lokale LAB gjenerojnë sinjalet e kontrollit në të gjithë LAB. Një rrjet i orës me anim të ulët shpërndan sinjale globale në orët e rreshtit [5..0]. Ndërlidhja MultiTrack përbëhet nga linja rrugëtimi të vazhdueshme, të optimizuara për performancën, me gjatësi dhe shpejtësi të ndryshme, të përdorura për efikasitetin e rrugëtimit. Përpiluesi Intel Quartus Prime drejton automatikisht shtigjet kritike të projektimit në ndërlidhje më të shpejta për të përmirësuar performancën e dizajnit dhe optimizon burimet e pajisjes.

Kontrolli i pastër logjik

Sinjalet në të gjithë LAB kontrollojnë logjikën për sinjalin e qartë të regjistrit ALM. Regjistri ALM drejtpërsëdrejti mbështet një klishe sinkron dhe asinkron. Çdo LAB mbështet një sinjal sinkron të qartë dhe dy sinjale të qarta asinkrone.

Pajisjet Intel Agilex ofrojnë një kunj rivendosjeje në të gjithë pajisjen (DEV_CLRn) që rivendos të gjithë regjistrat në pajisje. Mund të aktivizoni pinin DEV_CLRn në softuerin Intel Quartus Prime përpara përpilimit. Sinjali i rivendosjes në të gjithë pajisjen anashkalon të gjitha sinjalet e tjera të kontrollit.

Figura 5. Sinjalet e kontrollit Intel Agilex LAB-Wide

ALM

Seksionet e mëposhtme mbulojnë burimet ALM, daljen ALM dhe mënyrat e funksionimit ALM.

Burimet ALM

Çdo ALM përmban një shumëllojshmëri burimesh të bazuara në LUT që mund të ndahen midis dy LUT-ve adaptive kombinimi (ALUT), një grumbulluesi të plotë me dy bit dhe katër regjistrave.

Me deri në tetë hyrje për dy ALUT-të e kombinuara, një ALM mund të zbatojë kombinime të ndryshme të dy funksioneve. Kjo përshtatshmëri lejon që një ALM të jetë plotësisht e përputhshme me katër arkitektura LUT hyrëse. Një ALM mund të zbatojë gjithashtu një nëngrup prej tetë funksionesh hyrëse.

Një ALM përmban katër regjistra të programueshëm. Çdo regjistër ka portat e mëposhtme:

- Të dhënat në

- Të dhënat jashtë

- Ora normale LAB

- Ora LAB me vonesë

- Aktivizo orën

- Sinkron i qartë

- Asinkron i qartë

Sinjalet globale, kunjat e hyrjes/daljes me qëllim të përgjithshëm (GPIO) ose çdo logjikë e brendshme mund të nxisin orën për të aktivizuar sinjalin, orën dhe sinjalet e kontrollit asinkron ose sinkron të qartë të një regjistri ALM. Sinjali i aktivizimit të orës ka përparësi ndaj sinjalit të rivendosjes sinkron.

Për funksionet e kombinuara, regjistrat anashkalohen dhe dalja e tabelës së kërkimit (LUT) dhe grumbulluesve drejtohet drejtpërdrejt në daljet e një ALM. Dy dalje të shpejta janë të disponueshme për 6 dalje LUT dhe 5 dalje LUT të poshtme për të anashkaluar mux-in e daljes dhe për t'u lidhur me një LAB tjetër për rregullimin e rrugës kritike.

Figura 6. Diagrami i bllokut të nivelit të lartë të Intel Agilex ALM

Dalja ALM

Dalja ALM

Rezultatet e përgjithshme të rrugëtimit në çdo ALM drejtojnë burimet e rrugëtimit lokal, rreshtor dhe kolonë. Gjashtë dalje ALM, duke përfshirë dy shtigje të shpejta të daljes, mund të drejtojnë lidhjet e rrugëtimit të kolonave, rreshtave ose lidhjeve të drejtpërdrejta.

Dalja LUT, mbledhësi ose regjistri mund të nxisë daljet ALM. Si LUT ose mbledhësi ashtu edhe regjistri ALM mund të largohen nga ALM njëkohësisht.

Paketimi i regjistrit përmirëson përdorimin e pajisjes duke lejuar që regjistri i palidhur dhe logjika e kombinuar të paketohen në një ALM të vetme. ALM gjithashtu mund të nxjerrë jashtë versionet e regjistruara dhe të paregjistruara të daljes LUT ose të grumbulluesit.

Figura e mëposhtme tregon lidhjen Intel Agilex ALM. Në redaktuesin e vetive të burimeve Intel Quartus Prime, e gjithë lidhja ALM është thjeshtuar. Disa rrugëzime do të drejtohen nga brenda nga softueri Intel Quartus Prime.

Figura 7. Detajet e lidhjes Intel Agilex ALM Mënyrat e funksionimit ALM

Mënyrat e funksionimit ALM

Intel Agilex ALM funksionon në cilindo nga mënyrat e mëposhtme:

- Mënyra normale

- Modaliteti i zgjeruar LUT

- Mënyra aritmetike

Modaliteti Normal

Modaliteti normal lejon që dy funksione të zbatohen në një Intel Agilex ALM, ose një funksion të vetëm deri në gjashtë hyrje.

Deri në tetë hyrje të të dhënave nga ndërlidhja lokale LAB janë hyrje në logjikën e kombinimit.

ALM mund të mbështesë disa kombinime të funksioneve plotësisht të pavarura dhe kombinime të ndryshme funksionesh që kanë hyrje të përbashkëta.

Përpiluesi Intel Quartus Prime zgjedh automatikisht hyrjet në LUT. ALM-të në modalitetin normal mbështesin paketimin e regjistrave.

Figura e mëposhtme tregon një kombinim të lidhjeve të ndryshme hyrëse për modalitetin LUT. Në dizajnin tuaj, softueri Intel Quartus Prime mund të caktojë emërtime të ndryshme hyrëse gjatë përpilimit.

Figura 8. ALM në modalitetin normal

Kombinimet e funksioneve me më pak hyrje se ato të paraqitura mbështeten gjithashtu. Për shembullample, mbështeten kombinimet e funksioneve me numrin e mëposhtëm të hyrjeve.

- 4 dhe 3

- 3 dhe 3

- 3 dhe 2

- 5 dhe 2

Për paketimin e dy funksioneve me 5 hyrje në një ALM, funksionet duhet të kenë të paktën dy hyrje të përbashkëta. Inputet e zakonshme janë dataa dhe datab. Kombinimi i një funksioni me 4 hyrje me një funksion me 5 hyrje kërkon një hyrje të përbashkët (ose dataa ose datab).

Në një pajisje me përdorim të rrallë, funksionet që mund të vendosen në një ALM mund të zbatohen në ALM të veçanta nga softueri Intel Quartus Prime për të arritur performancën më të mirë të mundshme. Ndërsa një pajisje fillon të mbushet, softueri Intel Quartus Prime përdor automatikisht potencialin e plotë të Intel Agilex ALM. Përpiluesi Intel Quartus Prime kërkon automatikisht funksione duke përdorur hyrje të zakonshme ose funksione plotësisht të pavarura për t'u vendosur në një ALM për të përdorur me efikasitet burimet e pajisjes. Përveç kësaj, mund të kontrolloni manualisht përdorimin e burimeve duke vendosur caktimet e vendndodhjes.

Figura 9. 6-Hyrja e modalitetit LUT në modalitetin normal

Figura 10. 3-Hyrja e modalitetit LUT në modalitetin normal

Figura 10. 3-Hyrja e modalitetit LUT në modalitetin normal

të dhënat dhe të dhënat b janë të disponueshme për paketimin e regjistrit.  Ju mund të zbatoni çdo funksion prej tre deri në gjashtë hyrje duke përdorur hyrjet e mëposhtme:

Ju mund të zbatoni çdo funksion prej tre deri në gjashtë hyrje duke përdorur hyrjet e mëposhtme:

- të dhënat

- datad0

- datac0

- datac1

- datad1

- dataf

- dataa dhe datab—ku dataa dhe datab ndahen në të dy LUT për të ofruar fleksibilitet për të zbatuar një funksion të ndryshëm në secilën LUT.

Të dyja hyrjet e të dhënave dhe të bazës së të dhënave mbështesin veçorinë e paketimit të regjistrave. Nëse aktivizoni veçorinë e paketimit të regjistrave, të dyja hyrjet e të dhënave dhe të bazës së të dhënave ose njëra prej hyrjeve anashkalojnë LUT dhe futen drejtpërdrejt në regjistër, në varësi të mënyrës së përdorur të regjistrit të paketuar. Për pajisjet Intel Agilex, mbështeten llojet e mëposhtme të mënyrave të regjistrimit të paketuar:

- LUT me 5 hyrje me 1 shteg regjistri të paketuar

- LUT me 5 hyrje me 2 shtigje regjistrash të paketuara

- Dy LUT me 3 hyrje me 2 shtigje regjistrash të paketuara

LUT me 3 hyrje me 2 shtigje regjistrash të paketuara ilustrohet në figurën e modalitetit LUT me 3 hyrje në modalitetin normal. Për pajisjet Intel Agilex, modaliteti LUT me 6 hyrje nuk e mbështet funksionin e paketimit të regjistrave.

Modaliteti i zgjeruar LUT

Figura 11. Funksionet e mbështetura me 8 hyrje në modalitetin LUT të zgjeruar

Disa funksione me 8 hyrje mund të zbatohen në një ALM të vetme duke përdorur të gjitha hyrjet LUT:

- të dhënat

- datad0

- datac0

- dataa

- të dhënave

- datac1

- datad1

- dataf

Në modalitetin LUT të zgjeruar me 8 hyrje, mbështetet modaliteti i regjistrit të paketuar, me kusht që regjistri i paketuar të ndajë një hyrje të të dhënave ose të bazës së të dhënave me LUT me 8 hyrje.

Mënyra aritmetike

ALM në modalitetin aritmetik përdor dy grupe me dy LUT me 4 hyrje së bashku me dy grumbullues të plotë të dedikuar. Shtuesit e dedikuar lejojnë LUT-të të kryejnë logjikën para-mbledhëse. Prandaj, çdo grumbullues mund të shtojë daljen e dy funksioneve me 4 hyrje.

Modaliteti aritmetik ofron gjithashtu aktivizimin e orës, aktivizimin e numëratorit, kontrollin sinkron lart e poshtë, kontrollin e shtimit dhe zbritjes dhe pastrimin sinkron.

Opsionet e fshirjes dhe aktivizimit të orës janë sinjale në të gjithë LAB që prekin të gjithë regjistrat në LAB. Ju mund t'i çaktivizoni ose aktivizoni individualisht këto sinjale për çdo palë regjistrash në një LUT adaptive (ALUT). Softueri Intel Quartus Prime vendos automatikisht çdo regjistër që nuk përdoret nga numëruesi në LAB të tjerë.

Figura 12. Intel Agilex ALM në modalitetin aritmetik

Mbaj zinxhir

Mbaj zinxhir

Zinxhiri i bartjes siguron një funksion të shpejtë të bartjes midis grumbulluesve të dedikuar në modalitetin aritmetik.

Veçoria e përzgjedhjes së bartjes me 2 bit në pajisjet Intel Agilex ndan vonesën e përhapjes së zinxhirëve të transportit me ALM. Zinxhirët e bartjes mund të fillojnë ose në ALM-në e parë ose në ALM-në e gjashtë në një LAB. Sinjali përfundimtar i përcjelljes drejtohet në një ALM, ku furnizohet me ndërlidhjet lokale, rreshtash ose kolonash.

Udhëzuesi i përdorimit të Historisë së Rishikimit të Dokumentit për blloqet e grupit logjik të Intel Agilex dhe modulet e logjikës adaptive

| Versioni i dokumentit | Ndryshimet |

| 2022.05.24 | Figura e përditësuar: Diagrami i bllokut i nivelit të lartë të Intel Agilex ALM. |

| 2019.11.14 | Përditësuar përshkrimin në seksionin e sinjaleve të kontrollit LAB. |

| 2019.10.01 |

|

| 2019.04.02 | Lëshimi fillestar. |

Korporata Intel.

Të gjitha të drejtat e rezervuara. Intel, logoja e Intel dhe markat e tjera Intel janë marka tregtare të Intel Corporation ose filialeve të saj. Intel garanton performancën e produkteve të saj FPGA dhe gjysmëpërçuese sipas specifikimeve aktuale në përputhje me garancinë standarde të Intel, por rezervon të drejtën të bëjë ndryshime në çdo produkt dhe shërbim në çdo kohë pa paralajmërim. Intel nuk merr përsipër asnjë përgjegjësi ose përgjegjësi që rrjedh nga aplikimi ose përdorimi i ndonjë informacioni, produkti ose shërbimi të përshkruar këtu, përveçse kur është rënë dakord shprehimisht me shkrim nga Intel. Klientët e Intel këshillohen të marrin versionin më të fundit të specifikimeve të pajisjes përpara se të mbështeten në çdo informacion të publikuar dhe përpara se të bëjnë porosi për produkte ose shërbime.

*Emra dhe marka të tjera mund të pretendohen si pronë e të tjerëve.

ISO

9001:2015

I regjistruar

Dokumentet / Burimet

|

Intel Agilex Logic Array Blloqe dhe Modulet Adaptive Logic [pdfUdhëzuesi i përdoruesit Blloqe të vargjeve logjike Agilex dhe module logjike adaptive, Agilex, blloqe të grupeve logjike dhe module logjike adaptive, blloqe të grupeve dhe module logjike përshtatëse, module logjike përshtatëse, module logjike |