Intel-Level High-Level Synthesis Compiler Pro Edition

Informacioni i produktit

| Emri i produktit | Edicioni Pro i Përpiluesit të Sintezës së Nivelit të Lartë Intel |

|---|---|

| Versioni | 22.4 |

| Data e publikimit | 19 dhjetor 2022 |

| Njoftim për zhvlerësim | Është planifikuar të jetë përpiluesi i sintezës së nivelit të lartë Intel i zhvlerësuar pas versionit 23.4. |

Udhëzimet e përdorimit të produktit

Udhëzues për fillimin

- Inicializoni mjedisin tuaj të përpiluesit.

- Review dizajn të ndryshëm p.shampmësime dhe mësime të ofruara me përpiluesin Intel HLS.

Udhëzues përdorimi

- Udhëzuesi i Përdoruesit ofron udhëzime mbi

- Sintetizimi, verifikimi dhe simulimi i pronësisë intelektuale (IP) të krijuar për produktet Intel FPGA.

- Duke kaluar nëpër të gjithë rrjedhën e zhvillimit të komponentit tuaj, nga krijimi i komponentit dhe panelit të testimit tuaj deri te integrimi i IP-së së komponentit tuaj në një sistem më të madh me softuerin Intel Quartus Prime.

Udhëzuesi i praktikave më të mira

Udhëzuesi i praktikave më të mira ofron teknika dhe praktika që mund të aplikoni për të përmirësuar përdorimin e zonës FPGA dhe performancën e komponentit tuaj HLS. Zbatoni këto praktika më të mira pasi të keni verifikuar korrektësinë funksionale të komponentit tuaj.

Manuali i referencës

Manuali i referencës ofron informacion referimi rreth veçorive të mbështetura nga përpiluesi Intel HLS. Gjeni detaje mbi opsionet e komandës Intel HLS Compiler, header files, pragma, atribute, makro, deklarata, argumente dhe biblioteka shabllonesh.

Shënime të lëshimit të përpiluesit të përpiluesit të nivelit të lartë të sintezës Intel® Versioni Pro Edition 22.4

- Shënimet e lëshimit të Intel® High Level Synthesis Compiler Pro Edition ofrojnë informacione të vonuara në lidhje me versionin 22.4 të përpiluesit të sintezës së nivelit të lartë të Intel-it.

Në pritje të zhvlerësimit të përpiluesit Intel HLS

- Për të mbajtur aksesin në veçoritë më të fundit të dizajnit të nivelit të lartë FPGA, optimizimet dhe shërbimet e zhvillimit, migroni modelet tuaja ekzistuese për të përdorur Komplet e veglave bazë të Intel oneAPI.

- Përpiluesi i sintezës së nivelit të lartë të Intel (HLS) është planifikuar të mos përdoret pas versionit 23.4.

- Vizitoni faqen e produktit Intel oneAPI për këshilla për migrimin ose shkoni te forumi i komunitetit të Dizajnit të Nivelit të Lartë Intel për çdo pyetje ose kërkesë.

Rreth Bibliotekës së Dokumentacionit të Edicionit Intel HLS Compiler Pro

- Dokumentacioni për Intel HLS Compiler Pro Edition është i ndarë në disa botime. Përdorni tabelën e mëposhtme për të gjetur botimin që përmban informacionin e Intel HLS Compiler Pro Edition që kërkoni:

Tabela 1. Biblioteka e Dokumentacionit të Përpiluesit Pro të Sintezës së Nivelit të Lartë të Intel

| Titulli dhe Përshkrimi | |

| Shënimet e publikimit

Ofron informacione të vonuara në lidhje me përpiluesin Intel HLS. |

Lidhje |

| Udhëzues për fillimin

Ngrihuni dhe funksiononi me përpiluesin Intel HLS duke mësuar se si të inicializoni mjedisin e përpiluesit tuaj dhe të rifilloniviewing dizajn të ndryshëm p.shampmësime dhe mësime të ofruara me përpiluesin Intel HLS. |

Lidhje |

| Udhëzues përdorimi

Ofron udhëzime për sintetizimin, verifikimin dhe simulimin e pronësisë intelektuale (IP) që ju projektoni për produktet Intel FPGA. Kaloni në të gjithë rrjedhën e zhvillimit të komponentit tuaj nga krijimi i komponentit dhe panelit të testimit deri te integrimi i IP-së së komponentit tuaj në një sistem më të madh me softuerin Intel Quartus Prime. |

Lidhje |

| Udhëzuesi i praktikave më të mira

Ofron teknika dhe praktika që mund të aplikoni për të përmirësuar përdorimin e zonës FPGA dhe performancën e komponentit tuaj HLS. Në mënyrë tipike, ju i zbatoni këto praktika më të mira pasi të verifikoni korrektësinë funksionale të komponentit tuaj. |

Lidhje |

| Manuali i referencës

Ofron informacion referencë për veçoritë e mbështetura nga përpiluesi Intel HLS. Gjeni detaje mbi opsionet e komandës Intel HLS Compiler, header files, pragma, atribute, makro, deklarata, argumente dhe biblioteka shabllonesh. |

Lidhje |

Korporata Intel. Të gjitha të drejtat e rezervuara. Intel, logoja e Intel dhe markat e tjera Intel janë marka tregtare të Intel Corporation ose filialeve të saj. Intel garanton performancën e produkteve të saj FPGA dhe gjysmëpërçuese sipas specifikimeve aktuale në përputhje me garancinë standarde të Intel, por rezervon të drejtën të bëjë ndryshime në çdo produkt dhe shërbim në çdo kohë pa paralajmërim. Intel nuk merr përsipër asnjë përgjegjësi ose përgjegjësi që rrjedh nga aplikimi ose përdorimi i ndonjë informacioni, produkti ose shërbimi të përshkruar këtu, përveçse kur është rënë dakord shprehimisht me shkrim nga Intel. Klientët e Intel këshillohen të marrin versionin më të fundit të specifikimeve të pajisjes përpara se të mbështeten në çdo informacion të publikuar dhe përpara se të bëjnë porosi për produkte ose shërbime.

*Emra dhe marka të tjera mund të pretendohen si pronë e të tjerëve.

Në pritje të zhvlerësimit të përpiluesit Intel HLS

- Për të mbajtur aksesin në veçoritë më të fundit të dizajnit të nivelit të lartë FPGA, optimizimet dhe shërbimet e zhvillimit, migroni modelet tuaja ekzistuese për të përdorur Komplet e veglave bazë të Intel oneAPI.

- Përpiluesi i sintezës së nivelit të lartë të Intel (HLS) është planifikuar të mos përdoret pas versionit 23.4.

- Vizitoni faqen e produktit Intel oneAPI për këshilla për migrimin ose shkoni te forumi i komunitetit të Dizajnit të Nivelit të Lartë Intel për çdo pyetje ose kërkesë.

Karakteristikat dhe përmirësimet e reja

- Versioni 22.4 i Përpiluesit të Sintezës së Nivelit të Lartë Intel Pro Edition XNUMX përfshin veçoritë e reja të mëposhtme:

- Lirimi i mirëmbajtjes.

- Nuk ka veçori ose përmirësime të reja për Intel HLS Compiler Pro Edition Version 22.4.

Ndryshimet në sjelljen e softuerit

- Ky seksion dokumenton raste kur veçoritë e Intel HLS Compiler Pro Edition Version 22.4 kanë ndryshuar nga versionet e mëparshme të përpiluesit.

Lirimi i mirëmbajtjes.

- Nuk ka ndryshime në sjelljen e softuerit për Intel HLS Compiler Pro Edition Version 22.4.

Parakushtet Intel-level High-Level Synthesis Compiler Pro Edition

- Intel HLS Compiler Pro Edition është pjesë e Intel Quartus® Prime Pro Edition Design Suite. Mund ta instaloni përpiluesin Intel HLS si pjesë e instalimit të softuerit Intel Quartus Prime ose ta instaloni veçmas. Kërkon Intel Quartus Prime dhe softuer shtesë për t'u përdorur.

- Për udhëzime të hollësishme rreth instalimit të softuerit Intel Quartus Prime Pro Edition, duke përfshirë kërkesat e sistemit, parakushtet dhe kërkesat e licencimit, shihni Instalimi dhe Licencimi i Softuerit Intel FPGA.

- Përpiluesi Intel HLS kërkon softuerin e mëposhtëm përveç Intel Quartus Prime:

Përpiluesi C++

- Në Linux, Intel HLS Compiler kërkon GCC 9.3.0 duke përfshirë bibliotekën GNU C++ dhe shërbimet binare (binutils).

- Ky version i GCC ofrohet si pjesë e instalimit të përpiluesit tuaj Intel HLS. Pas instalimit të përpiluesit Intel HLS, GCC 9.3.0 është i disponueshëm në /gcc.

- E rëndësishme: Përpiluesi Intel HLS përdor Drejtoria /gcc si direktoria e saj e zinxhirit të veglave. Përdoreni këtë instalim të GCC për të gjithë punën tuaj të projektimit të lidhur me HLS.

- Për Windows, instaloni një nga versionet e mëposhtme të Microsoft* Visual Studio* Professional:

- Microsoft Visual Studio 2017 Professional

- Komuniteti i Microsoft Visual Studio 2017

- Për mbështetjen më të përditësuar të C++17, sigurohuni që po përdorni versionin më të fundit të Visual Studio 2017.

- E rëndësishme: Softueri Intel HLS Compiler nuk mbështet versione të Microsoft Visual Studio përveç atyre të specifikuara për edicionin e softuerit.

Siemens* EDA Questa® Software simulimi

- Në sistemet Windows dhe RedHat Linux, mund të instaloni softuerin e simulimit Questa® nga instaluesi i softuerit Intel Quartus Prime. Opsionet e disponueshme janë si më poshtë:

- Questa Intel FPGA Edition

- Questa Intel FPGA Starter Edition

- Si Questa Intel FPGA Edition ashtu edhe Questa Intel FPGA Starter Edition kërkojnë licenca. Licenca për Questa Intel FPGA Starter Edition është falas. Për detaje, referojuni Instalimit dhe Licencimit të Softuerit Intel FPGA.

- Përndryshe, mund të përdorni versionin tuaj të licencuar të softuerit Siemens* EDA ModelSim* SE ose Siemens EDA Questa Advanced Simulator.

- Në sistemet Linux, Questa – Intel FPGA Edition dhe Questa – Intel FPGA Starter Edition kërkojnë paketat e mjeteve të zhvillimit Red Hat*.

- Për informacion në lidhje me të gjitha versionet e softuerit ModelSim dhe Questa që mbështet softueri Intel, referojuni seksionit Informacioni i ndërfaqes EDA në Shënimet e lëshimit të mbështetjes së softuerit dhe pajisjes për versionin tuaj të Intel Quartus Prime Pro Edition.

Informacione të Përafërta

- Udhëzues për fillimin e përpiluesit të sintezës së nivelit të lartë të Intel

- Sistemet operative të mbështetura

- Kërkesat e softuerit në instalimin dhe licencimin e softuerit Intel FPGA

- Informacioni i ndërfaqes EDA (Intel Quartus Prime Pro Edition)

Çështje të njohura dhe zgjidhje

- Ky seksion ofron informacion rreth çështjeve të njohura që prekin versionin 22.4 të Intel HLS Compiler Pro Edition.

| Përshkrimi | Zgjidhje |

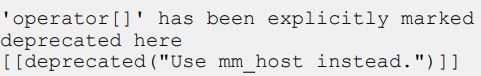

| Kur përdorni klasën e vjetëruar mm_master, përpiluesi lëshon një mesazh paralajmërues si më poshtë:

Ky mesazh nuk tregon se cila pjesë e kodit tuaj duhet të ndryshojë. |

Shmangni këtë mesazh paralajmërues duke përdorur klasën mm_host, e cila zëvendëson klasën e vjetëruar mm_master. |

| (Vetëm Windows) Përpilimi i një dizajni në një direktori me një emër të rrugës së gjatë mund të rezultojë në dështime të përpilimit.

Kontrolloni debug.log file sepse “nuk gjeta dot file” gabime. Këto gabime mund të tregojnë se rruga juaj është shumë e gjatë. |

Përpiloni dizajnin në një drejtori me një emër të shkurtër të rrugës. |

| (vetëm Windows) Një rrugë e gjatë për direktorinë tuaj të instalimit të Intel Quartus Prime mund t'ju pengojë të përpiloni dhe ekzekutoni me sukses udhëzimet e përpiluesit të Intel HLS dhe ishample dizajne.

Kontrolloni debug.log file sepse “nuk gjeta dot file” gabime. Këto gabime mund të tregojnë se rruga juaj është shumë e gjatë. |

Zhvendosni mësimet dhe pshamples në një emër të shkurtër shtegu përpara se të përpiqeni t'i ekzekutoni ato. |

| Përshkrimi | Zgjidhje |

| Bibliotekat që synojnë OpenCL* dhe janë të shkruara në HLS nuk mund të përdorin rrjedha ose tuba si një ndërfaqe midis kodit OpenCL dhe bibliotekës së shkruar në HLS.

Megjithatë, biblioteka në HLS mund të përdorë rrjedha ose tubacione nëse të dyja pikat fundore janë brenda bibliotekës (p.sh.ample, një rrjedhë që lidh dy funksione detyrash). |

N/A |

| Aplikimi i parametrit ihc::maxburst në ndërfaqet pritëse të Avalon® Memory-Mapped mund të bëjë që dizajni juaj të varet në simulim. | N/A |

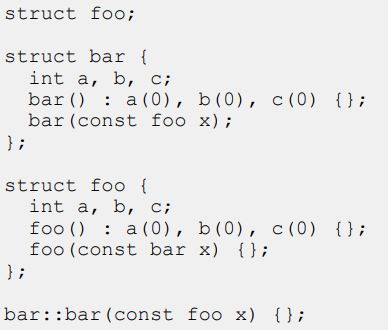

| Në disa raste të pazakonta, nëse keni dy klasa, ndërtuesit e të cilave secili kërkojnë shembuj të klasës tjetër si hyrje, përpiluesi mund të rrëzohet.

Për shembullampLe, përpilimi i copës së kodit të mëposhtëm shkakton rrëzimin e përpiluesit:

|

Shmangni krijimin e një përkufizimi rrethor. Në vend të kësaj, përdorni një tregues ose referencë në konstruktorin tuaj të kopjes.

Për shembullample, transformoni fragmentin e mëparshëm të kodit në kodin e mëposhtëm dhe kaloni në struct si një referencë për konstruktorin:

|

| Bibliotekat që synojnë OpenCL dhe janë të shkruara në HLS mund të bëjnë që kernelet OpenCL që përfshijnë bibliotekën të kenë një përmbledhje shtesë më konservatore. | N/A |

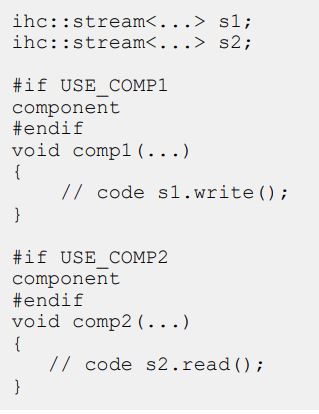

| Kur zhvilloni një bibliotekë, nëse keni një #define që përcakton një vlerë që përdorni më vonë në një #pragma, komanda fpga_crossgen dështon.

Për shembullample, kodi i mëposhtëm nuk mund të përpilohet nga

|

Përdorni pragmën në vend të #pragmës.

Për shembullample, në vijim përpilohet me sukses me

|

| Kur përdorni opsionin e komandës -c për të patur një përmbledhje dhe lidhje të veçantëtages në rrjedhën tuaj të punës, dhe nëse nuk e specifikoni opsionin -marsh në lidhjen stage (ose specifikoni një vlerë të ndryshme opsioni -marsh), lidhja juaj stage mund të dështojë me ose pa mesazhe gabimi. | Sigurohuni që të përdorni të njëjtën vlerë opsioni -marsh si për përpilimin me opsionin e komandës -c stage dhe s-ja lidhësetage. |

| Përshkrimi | Zgjidhje |

| Zbatimi i atributit të memories hls_merge në një grup të deklaruar brenda një cikli të shpalosur ose pjesërisht të shpalosur bën që kopjet e grupit të bashkohen nëpër përsëritjet e ciklit të shpalosur.

|

Shmangni përdorimin e atributit të memories hls_merge në unazat e hapura.

Nëse keni nevojë të bashkoni memoriet në një lak të zbërthyer, deklaroni në mënyrë eksplicite një grup të tipit struct për bashkimin e gjerësisë ose deklaroni një grup më të thellë për bashkimin në thellësi.

|

| Në memorien e funksionit ViewNë raportin e dizajnit të nivelit të lartë, disa kujtime me shtrirje funksioni mund të duken si "të optimizuara larg". | Asnjë.

Kur a file përmban funksione që janë komponentë dhe funksione që nuk janë komponentë, të gjitha variablat me shtrirje funksioni janë të listuara në panelin "Function Memory List", por vetëm variablat nga komponentët kanë informacion rreth tyre për t'u shfaqur në "Memoria e funksionit". View panel. |

| Disa raporte të dizajnit të nivelit të lartë dështojnë në Microsoft Internet Explorer*. | Përdorni një nga shfletuesit e mëposhtëm për të view raportet:

• Google Chrome* • Microsoft Edge* • Mozilla* Firefox* |

| Loop Viewnë Raportet e Dizajnit të Nivelit të Lartë ka kufizimet e mëposhtme:

• Sjellja e grupimeve pa stallë nuk është modeluar në Loop Viewer. Vonesa përfundimtare e treguar në Loop ViewPër një grup pa stalla është zakonisht më pesimist (d.m.th., më i lartë) sesa vonesa aktuale e dizajnit tuaj. Për një përshkrim të grupimeve dhe grupimeve pa stalla, referojuni Grumbullimi i shtegut të të dhënave në Intel i nivelit të lartë Udhëzuesi i praktikave më të mira të Synthesis Compiler Pro Edition. • Stallat nga leximet dhe shkrimet nga kujtesa ose deklaratat e shtypura nuk janë modeluar. • Numërimet me përsëritje të lartë (>1000) shkaktojnë performancë të ngadaltë të Loop Viewer. • Nuk mund të specifikoni një numër përsëritjesh prej zero (0) në Loop Viewer. |

Asnjë. |

| Lidhjet në disa raporte në Raportet e Dizajnit të Nivelit të Lartë të krijuara në sistemet Windows nuk funksionojnë. | Gjeneroni Raportet e Dizajnit të Nivelit të Lartë (d.m.th., përpiloni kodin tuaj) në një sistem Linux. |

| Përdorimi i një strukture të një lloji të vetëm të të dhënave ac_int në një ndërfaqe steaming që përdor pako (ihc::usesPackets ) nuk punon.

Për shembullample, pjesa e mëposhtme e kodit nuk funksionon:

|

Për të përdorur këtë kombinim në dizajnin tuaj, respektoni kufizimet e mëposhtme:

• Madhësia e brendshme e të dhënave ac_int duhet të jetë shumëfish i 8 • Deklarata e llojit të ndërfaqes së transmetimit duhet të specifikojë ihc::bitsPerSymbol<8> Për shembullample, pjesa e mëposhtme e kodit funksionon:

|

| Përshkrimi | Zgjidhje | |

| Kur ekzekutoni një simulim të performancës së lartë të komponentit tuaj duke përdorur thirrjet e funksionit në radhë, nëse nuk përdorni funksionin ihc_hls_component_run_all për të ekzekutuar thirrjet e komponentit të rreshtuar pas të gjitha thirrjeve të ihc_hls_enqueue për atë komponent, ndodhin sjelljet e mëposhtme:

• Në emulim, funksionet e komponentit të vendosur në radhë ekzekutohen. • Në simulim, funksionet e komponentëve në radhë nuk ekzekutohen, pa dhënë asnjë mesazh gabimi ose paralajmërimi. |

Sigurohuni që të përdorni funksionin ihc_hls_component_run_all pasi të gjitha thirrjet ihc_hls_enqueue që ai komponent të ekzekutojë thirrjet e funksioneve të rreshtuara në radhë. | |

| Nisja e një funksioni detyrë me ihc::launch_always_run | Për të shmangur heqjen e optimizimit, shtoni një kohë (1) | |

| heq atributet e optimizimit të aplikuara në detyrë | lak në funksionin e prekur aplikoni kontrollin përkatës | |

| funksionin. | pragma në ciklin while(1) në vend të funksionit. | |

| Në kodin e mëposhtëm p.shample, atributi i aplikuar në funksion injorohet. Raportet e projektimit të nivelit të lartë tregojnë një II nga 1 për këtë detyrë në vend të II të kërkuar nga 4. | Kodi i mëposhtëm p.shamptregoni se si mund ta zbatoni këtë ndryshim për kodin e mëparshëm p.shampe: | |

|

|

|

| Për projektet Cyclone® V që përmbajnë komponentë të shumtë HLS, kur përdorni komandën i++ për të përpiluar projektin tuaj në harduer (i++ -march=CycloneV), mund të merrni një gabim.

Ndërsa teksti i gabimit ndryshon në varësi të projektit tuaj, nënshkrimi i gabimit është një dështim i përpilimit të Intel Quartus Prime për shkak të sintaksës së keqe Verilog. Një modul përpiqet të përdorë një funksion që përpiluesi Intel Quartus Prime nuk mund ta gjejë. |

Nëse hasni këtë problem, vendosni çdo komponent HLS në një projekt të veçantë. | |

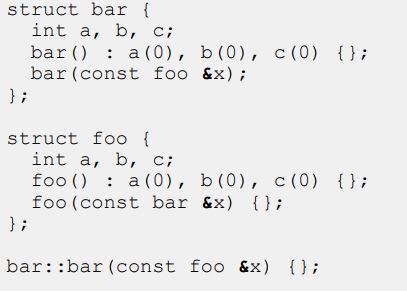

| Përpilimi i disa modeleve që përmbajnë komponentë të shumtë gjeneron një gabim në lidhje me ripërdorimin e transmetimit. | Nëse hasni këtë problem, përpiloni secilin komponent në dizajn veç e veç. Mund t'ju duhet të shtoni makro në kodin tuaj për të mundësuar që secili komponent të përpilohet veçmas. | |

| Merrni parasysh shembullin e mëposhtëmampe: | ||

|

||

Arkivi i shënimeve të publikimit të përpiluesit të nivelit të lartë të Intel-it

Për versionet më të fundit dhe të mëparshme të këtij udhëzuesi të përdorimit, referojuni Intel HLS Compiler Pro Edition Release Notes. Nëse një version i softuerit nuk është i listuar, zbatohen shënimet e lëshimit për versionin e mëparshëm të softuerit.

Historia e rishikimit të dokumentit për Intel HLS Compiler Pro Edition Version 22.4 Shënime të publikimit

| Versioni i dokumentit | Versioni i Intel Quartus Prime | Ndryshimet |

| 2022.12.19 | 22.4 | • Lëshimi fillestar. |

Dokumentet / Burimet

|

Intel High Level Synthesis Compiler Pro Edition [pdfUdhëzime Version 22.4, Version 23.4, High Level Synthesis Compiler Pro Edition, High Level Synthesis Compiler, Pro Edition |